来自@熵增

发表于:泰拉技术协会

原帖地址:电路:三种乘法器原理讲解

1.行波进位乘法器(单周期)

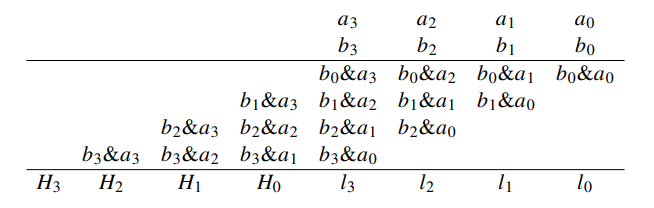

乘法是加法的推广,乘法器也是加法器的推广。我们首先来看二进制乘法的竖式计

算。因为乘法规模较大,这里给出 4 位乘法的例子。

乘法竖式计算

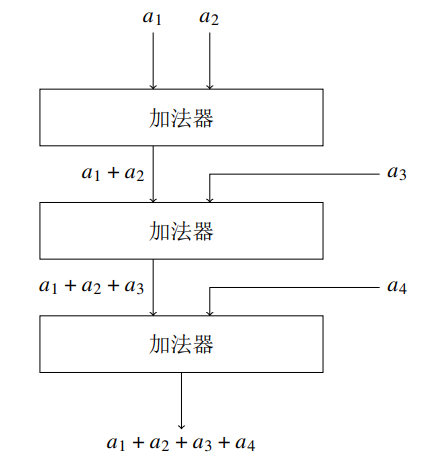

从上图可以看出来,做一个 4 位乘法实际上就是做 4 个数的加法。4 个数的加法,

可以按照运算顺序拆分成三次 2 个数的加法,如下图所示。

四个加数 𝑎1, 𝑎2, 𝑎3, 𝑎4 连加

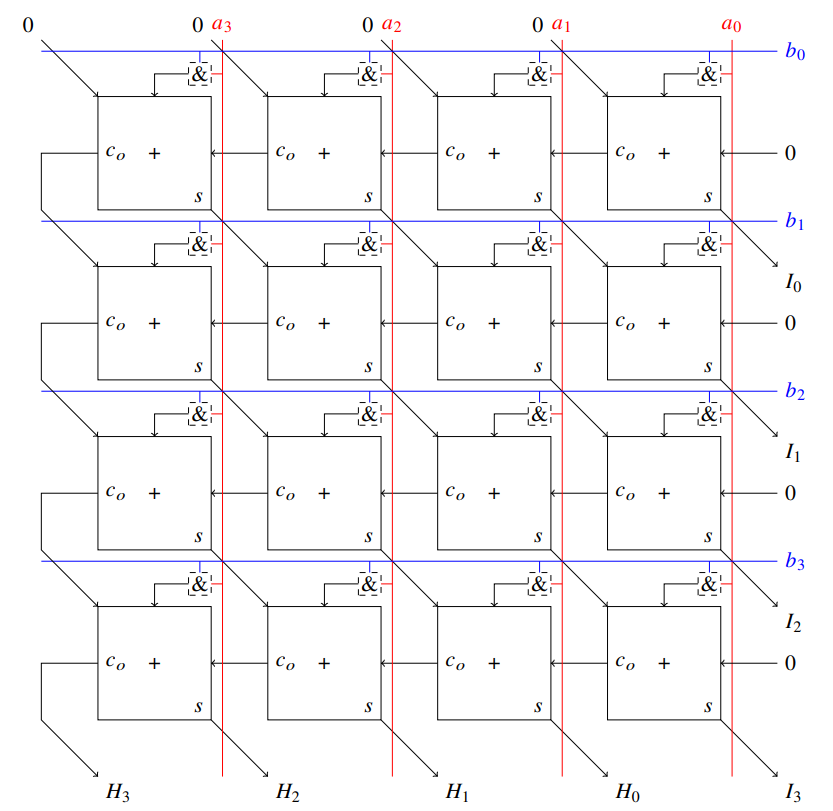

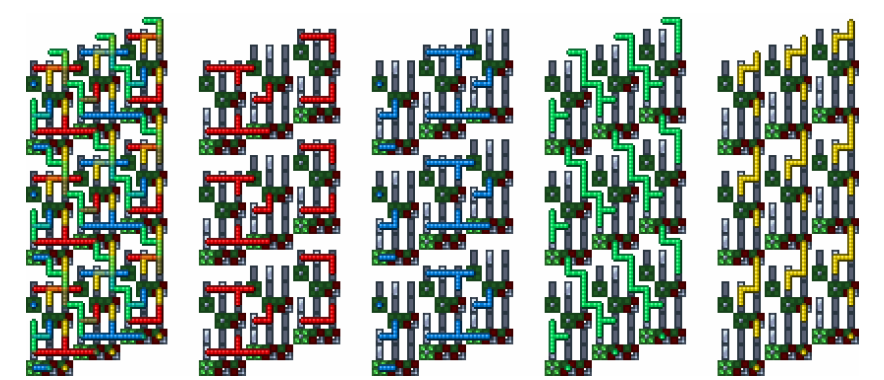

把之前贴子中的加法器展开成串联的全加器,就得到了四位乘法器的结构示意图。

四位乘法器结构示意图。大的实线方框表示全加器,𝑐𝑜 表示进位输出,𝑠 表示和输出。小

的虚线方框表示与门,红蓝线输入,黑线输出。两个乘数分别从上方和右方输入,乘积的低位从

右边输出,高位从下边输出。全加器缺少的输入补零。左右相邻的两个全加器,右边的早一个逻

辑帧;上下相邻的两个全加器,上边的早两个逻辑帧。

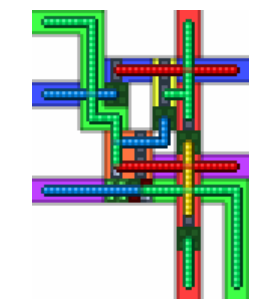

乘法器单个单元的结构

其中用不同颜色的背景墙标记区域和线路。橙色区域为全加器。黄色区域是与门。蓝色线路是从右边输入的乘数,每经过一个单元要延迟 1 个逻辑帧。红色线路是从上边输入的乘数,每经过一个单元要延迟 2 个逻辑帧。紫色线路是横向的进位传递。绿色线路是从左上到右下的和传递。

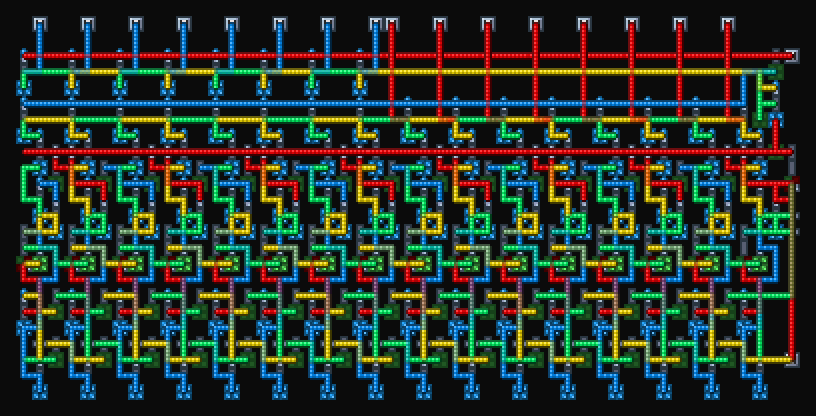

堆叠优化后的效果

其中每个单元大小 3*7。优化过程用到了如下的接线

技巧:

-左右方向上红蓝线循环,便于接线。

-相邻两列错位,便于进位和横向乘数的传递。

-纵向的逻辑延迟用到了一个异或门,从而这个门不需要为经过的绿线让路。

-与门利用了等式 𝑎&𝑏 = ˜𝑎𝑏&𝑏,便于接线。

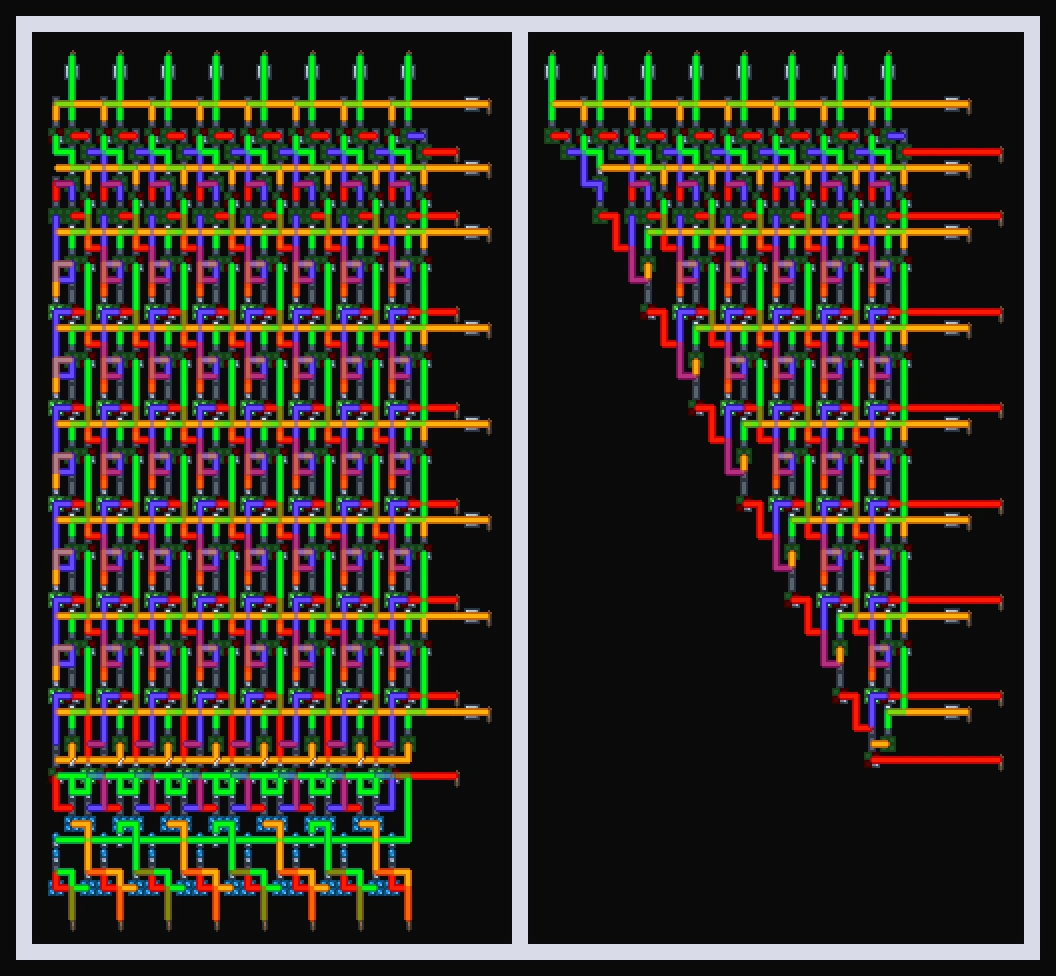

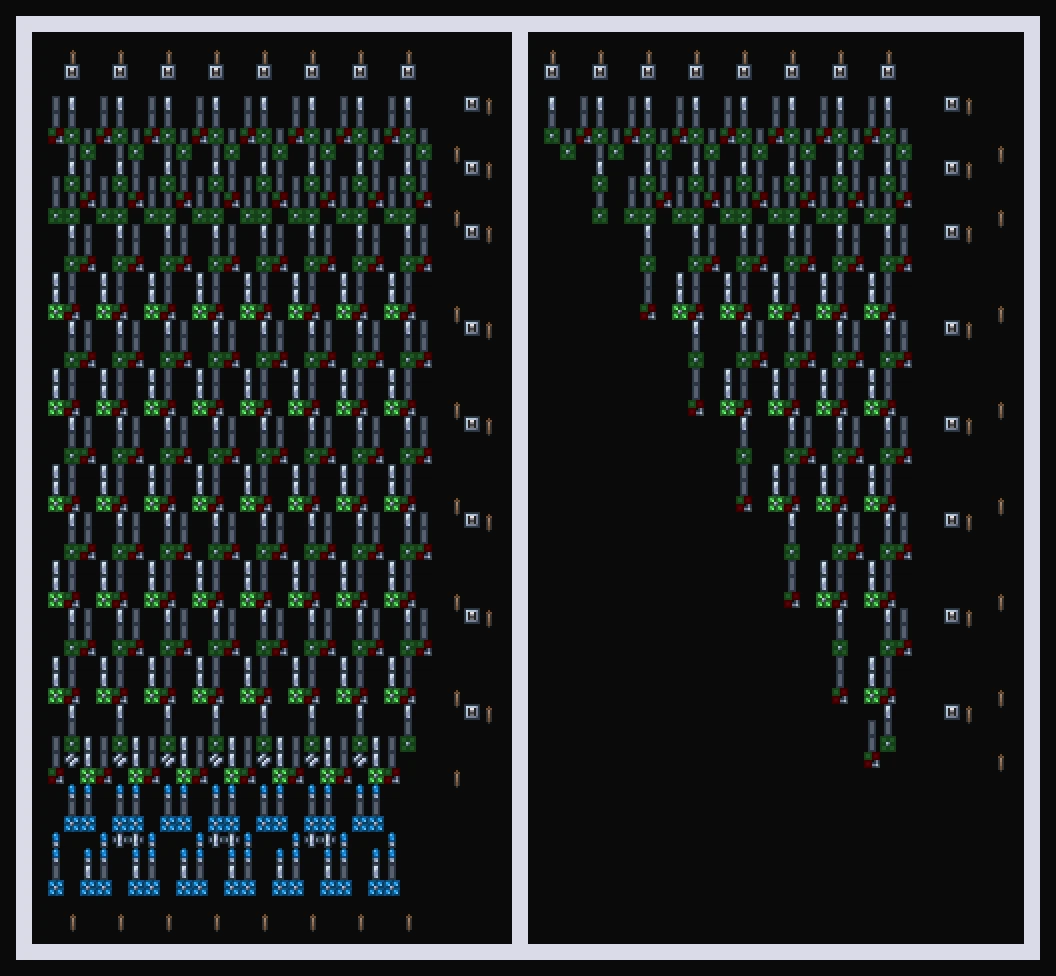

2.移位相加乘法器(多周期)

与前述单周期乘法器原理相同,但是使用驱动复用相同电路以减少面积,计算n位乘法需要n周期。

3.保存进位乘法器(单周期)

使用保留进位加法器(Carry Save Adder,CSA)代替行波进位加法器(Ripple Carry Adder,RCA)以减少面积。就单元面积来看仍然是3*7,但连接后呈矩形,不像行波进位乘法器呈平行四边形。矩形的模块较容易与其他模块配合使用。注意到下方使用并行输入串行输出的累加器代替行波进位加法器以减少面积,所以这是一个用时序逻辑部件模拟组合逻辑部件的电路。这是目前最小的单周期乘法器。

4.展望

多周期乘法器仍有压缩的空间,但使用通用的ALU代替专用的乘法器和除法器等模块显然是更好的选择。而按照现在原理的单周期乘法器可能已经压缩到了极限,继续压缩也不会有大幅的面积减少,所以可能需要提出新的原理来进一步压缩,比如使用booth编码或Wallace tree进一步压缩。但基于泰拉电路的特性,可能并不合适。

看不懂,但是感觉好nb