来自@熵增

发表于:泰拉技术协会

原帖地址:电路:泰拉瑞亚中最小的加法器的原理

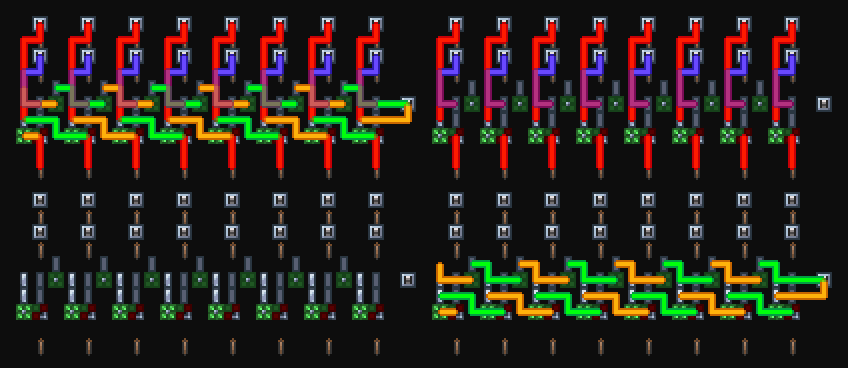

今天我们要讨论的是这种串行加法器,它在几年前被制作出来,直到现在仍然是泰拉瑞亚中最小和最常用的加法器。

相比于完全按照真值表制作的旧加法器,这种加法器每位只使用了两个逻辑门和两个逻辑灯。这种压缩肯定会让第一次看到的人一头雾水,感叹简直是神迹。直到现在,我仍然不知道它的作者是如何把它想出来的。

不过,我可以从成品出发,使用布尔代数和组合逻辑相关知识反推这种加法器符合全加器真值表的原理。

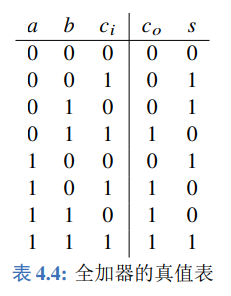

首先让我们先看一下全加器的真值表:

利用 TCLC,我们可以算出Co有四灯表示,S有单灯表示:

Co = ˆ(abCi, ˜Ci, ˜b, ˜a) = ˜ˆ(Ci, b, a, ˜abCi)

S = abCi

可见Co的逻辑表达式较为复杂,故我们可以采用不需要逻辑门的连接运算化简Co。

考虑CoS的真值表,我们可以算出CoS有双灯表示:

CoS = ˜aCi&˜ab = ˜bCi&˜ab = ˜bCi&˜aCi

这样一来,S仍用单灯表示,而Co使用双灯与单灯的连接:Co=CoSS = (CoS)S,我们就

得到了下图所示的电路:

注意到,为方便接线,abCi被替换为ˆ(ab, Ci) 。

这样,我们就得到了全加器的电路。将需要位数的全加器首尾相连即可完成加法器,而在每位全加器上添加对b的取反(即连接),并在最低位添加进位,即可完成减法运算。

那么是否存在更小的组合逻辑加法器呢?显然是没有的,由全加器的真值表可得,输出的数量为2,所以最少为两个逻辑门,秩的大小为2,所以需要两个逻辑灯。但是,如果加上时序逻辑,就会得到一种更小的加法器/累加器,不过其与其他电路配合较为困难,这就是另一篇文章要讲的事情了。

对于一般的电路玩家,只需要知道这种加法器的用法,而不需要知道它的原理即可完成电路,对于想要压缩电路的玩家,可以通过它的原理了解与其等价的电路,进而完成电路的压缩。

暂无回复内容

亲爱的馆友,老酒馆已暂停评论~

您可以前往新酒馆参与讨论!(๑•̀ㅂ•́)و✧

→ 点击查看酒馆重大版本更新公告